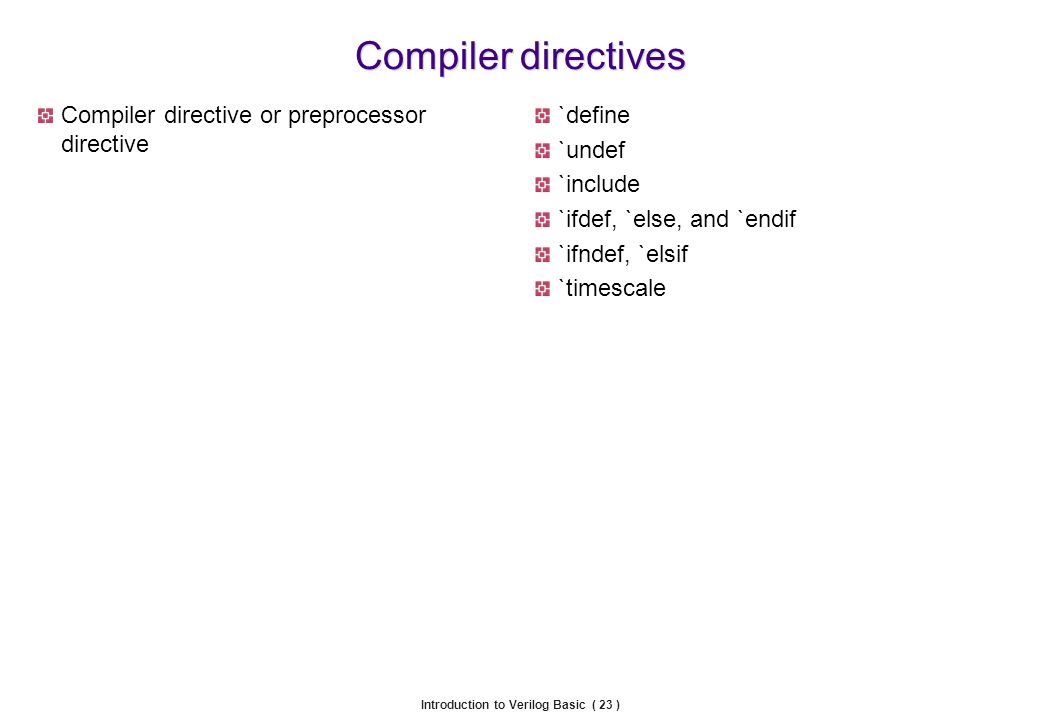

Verilog Compiler Directives the first defined // macro_name includes the source lines `else // include source lines3 when no prior macro_name defined // the source lines 3 `endif // end the construct `ifndef macro_name // like `ifdef except logic is reversed, // true if macro_name is undefined `timescale 1nsThis page contains Verilog tutorial, Verilog Syntax, Verilog Quick Reference, PLI, modelling memory and FSM, Writing Testbenches in Verilog, Lot of Verilog Examples and Verilog in One Day Tutorial Verilog Operators PartI Feb914 Equality Operators There are two types of Equality operatorsVerilog only supports `ifdef which means if something is defined at all, the code between the `ifdef statement and the `else or `endif will be executed, and if not only the code after the `else (if any) will be executed I think to do what you want you should be using

Chapter 42 Tips And Tricks

Verilog ifdef else

Verilog ifdef else-`endif `celldefine `endcelldefine Flags the Verilog source code between the two directives as a cellUsing the GUI to define the 'ifdef doesn't help I have verilog like 'ifdef PARAM_1 INST_ASIC_MEM_1 'elsif INST_ASIC_MEM_2 'else INST_FPGA_MEM In this case I want the 'else to be executed I have set the PARAM_1 & PARAM_2 to ZERO from the project settings, as suggested on this discussion FYI I am using 134 Vivado

Verilog If Else If

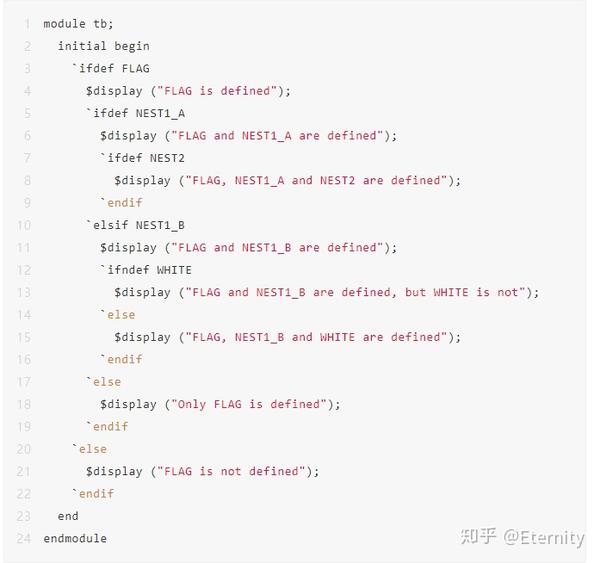

Ask Question Asked 8 years, 8 months ago Active 8 years, 8 months ago Viewed 15k times 6 I'm pretty sure I've done something like this in C before where I have a variety of choices but only one will be true at compile, and I'd like to do it for Verilog sims as well I haven't found anything about it though`ifdef `else `endif Optionally includes lines of source code during compilation The `ifdef directive checks that a macro has been defined, and if so, compiles the code that follows If the macro has not been define, VerilogXL compiles the code (if any) following the optional `else directiveIn Verilog, you can easily use the #ifdef preprocessor In VHDL, which is my first language, I can't replace it, specifically in this circumstance, with the generate statement which can't generate the parameters needed for the ports before starting anything in the block

An example PN check digit A PN consists of 10 digits d 1d 2d 3d 4d 5d 6d 7d 8d 9 d 10 d 10 is a check digit computed by the algorithm 10 9 10 10 2( ) 19 0 ( ) ( 1) (0) d S S S X d k S k k k = − = ⊕ = = − dIcarus verilog does not interpred the `ifdef `endif combo in the same way as the verilog XL and/or ncverilog igor@ld112/tmp> iverilog definev defineAAAA defineAAAA No such file or directory igor@ld112/tmp> /aout AAAA not defined igor@ld112/tmp> iverilog definev igor@ld112/tmp> /aout AAAA not defined Using the switch D the test code works OKActivity points 1,527 vhdl log2 #ifdef and macro expansion is a simple textreplacement, made by a preprocessor before the compiler sees the code Therefore, #ifdef is not limited to processing and generating legal syntax This makes it extremely versatile, at the cost of having no language knowledge at all

`elsif D01 reg t01;Its the conditional compilation directive that is used to include either optional or alternative lines of Verilog HDL source description during compilation The `ifdef checks for the definition of a macro If it is defined, then the lines following the `ifdef are included If the macro is not defined and an `else directive exists then itVerilog only supports `ifdef which means if something is defined at all, the code between the `ifdef statement and the `else or `endif will be executed, and if not only the code after the `else (if any) will be executed I think to do what you want you should be using

Verilog Basic Language Constructs Lexical Convention Data Types And So On Spring 09 Ppt Download

Prezentaciya Na Temu Verilog System Tasks Functions And Compiler Directives Ando Ki Spring 09 Skachat Besplatno I Bez Registracii

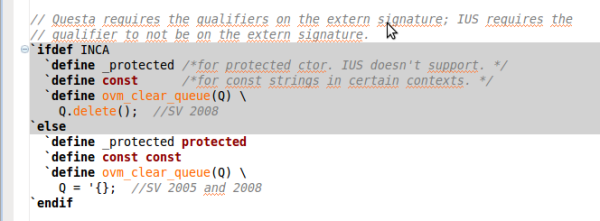

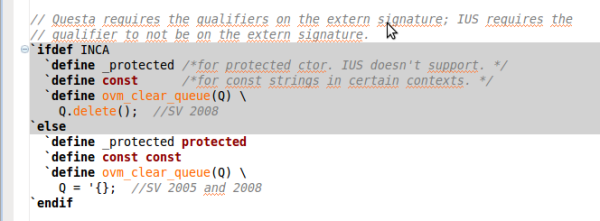

Verilog converted to html by v2html (written by Costas Calamvokis)The Verilog preprocessor was first standardized in Verilog , and has been improved with each subsequent standard Reviewing some of the changes Verilog 1995 `define MACRO `ifdef `else `endif `include Verilog 01 `define MACRO(arg) `ifndef `elsif `undef `line SystemVerilog 05 `` `" `\`" SystemVerilog 09Conditional compilation Allows Verilog source code to be optionally included, based on whether or not macro_name has been defined using `define or an invocation option Examples `ifdef RTL wire y = a & b;

Slides For Formal Verification Of Verilog Hdl With Yosys Smtbmc

Systemverilog与verilog中重定义问题解决方案 知乎

Hi I've just learned that in Verilog you can use an `ifdef statement that makes Quartus ignore the following code (until the next`endif) you can define a macro in the qsf file (or through the GUI) to decide which parts of code to ignore`ifndef U00 module should_be_true;Note that ifdef only tests whether a variable has a value It does not expand the variable to see if that value is nonempty Consequently, tests using ifdef return true for all definitions except those like foo = To test for an empty value, use ifeq ($(foo),) For example, bar = foo = $(bar) ifdef foo frobozz = yes else frobozz = no endif

Chapter 42 Tips And Tricks

Solved How To Define Verilog Macros In Vivado Community Forums

Code`define SYNTHESIS // Uncommented for synthesis (`define method 1) //`define SIMULATION //Uncommented for simulation `include some_headerv // Header file module33 Data types¶ Data types can be divided into two groups as follows, Net group Net group represents the physical connection between components eg wire, wand and wor etcIn the tutorials, we will use only one net data type ie 'wire', which is sufficient to create all types of designsThe #ifdef, #ifndef , #elseif, #elif, #else, and

0 件のコメント:

コメントを投稿